Researchers at Tohoku University and the University of California, Santa Barbara, have unveiled a probabilistic computer prototype. Manufacturable with a near-future technology, the prototype combines a complementary metal-oxide semiconductor (CMOS) circuit with a limited number of stochastic nanomagnets, creating a heterogeneous probabilistic computer.

Developing computers capable of efficiently executing probabilistic algorithms frequently used in artificial intelligence and machine learning is a challenge scientists have long sought to overcome. The approach outlined in this work presents a promising and feasible solution to address this, with the researchers confirming that its superior computational performance and energy-efficiency surpass current CMOS technology.

The details of this breakthrough were published in the journal Nature Communications on March 27, 2024.

Recent artificial intelligence and machine learning have had a transformational impact on societies. In such technology, probabilistic algorithms are utilized to solve problems where uncertainty is inherent or where an exact solution is computationally infeasible. These operations follow specific instructions within CMOS circuits, but sometimes there exist inconsistencies between how software (instructions) and hardware (circuits) work together, leading to discrepancies in outcomes.

As the role of artificial intelligence and machine learning expands, there is a strong demand for a new computing paradigm that reconciles this mismatch, achieving greater sophistication while significantly reducing energy consumption.

In this study, graduate student Keito Kobayashi and Professor Shunsuke Fukami from Tohoku University, along with Dr. Kerem Camsari from the University of California, Santa Barbara, and their colleagues, developed a near-future heterogeneous version of a probabilistic computer tailored for executing probabilistic algorithms and facile manufacturing.

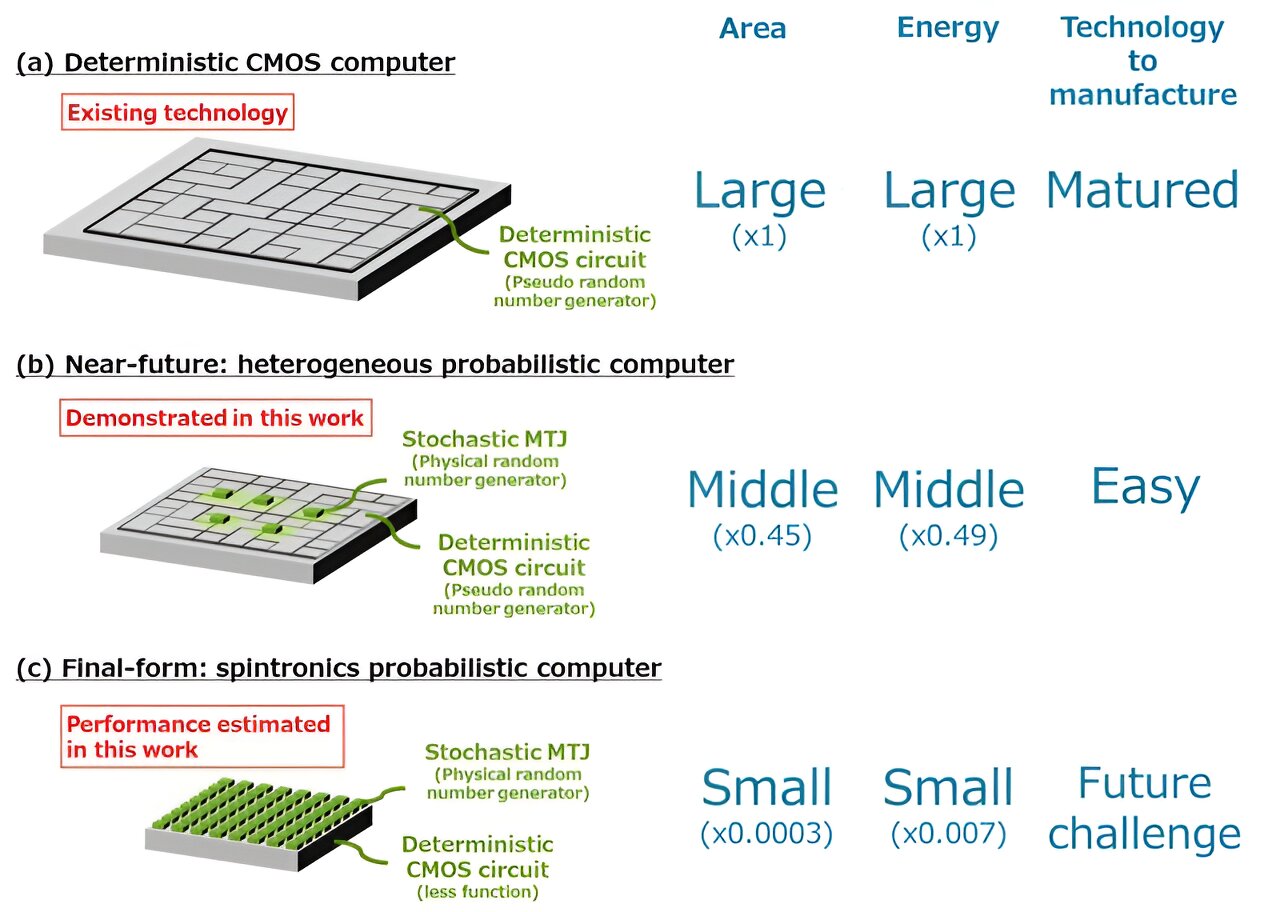

“Our constructed prototype demonstrated that excellent computational performance can be achieved by driving pseudo random number generators in a deterministic CMOS circuit with physical random numbers generated by a limited number of stochastic nanomagnets,” says Fukami. “Specifically speaking, a limited number of probabilistic bits (p-bits) with a stochastic magnetic tunnel junction (s-MTJ), should be manufacturable with a near-future integration technology.”

The researchers also clarified that the final form of the spintronics probabilistic computer, primarily composed of s-MTJs, will yield a four-order-of-magnitude reduction in area and a three-order-of-magnitude reduction in energy consumption compared to the current CMOS circuits when running probabilistic algorithms.

Ultimately, Fukami and his colleagues’ prototype addresses the limitations of current deterministic CMOS circuits for artificial intelligence and machine learning. “We anticipate future research and development will advance, leading to the implementation in society of an innovative computing hardware that boasts exceptional computational performance and energy-saving capabilities,” adds Fukami. https://techxplore.com/news/2024-04-energy-efficient-probabilistic-combining-cmos.html

Recent Comments