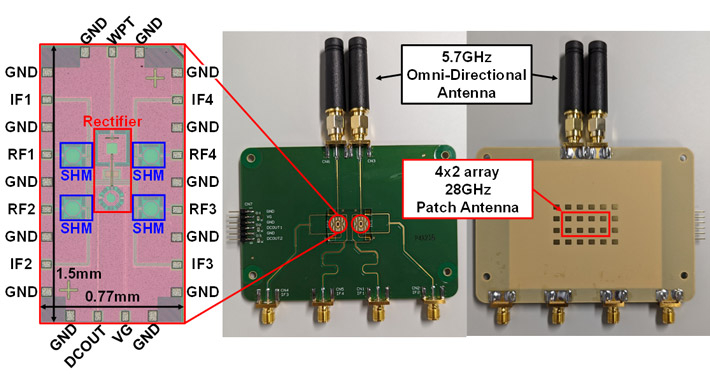

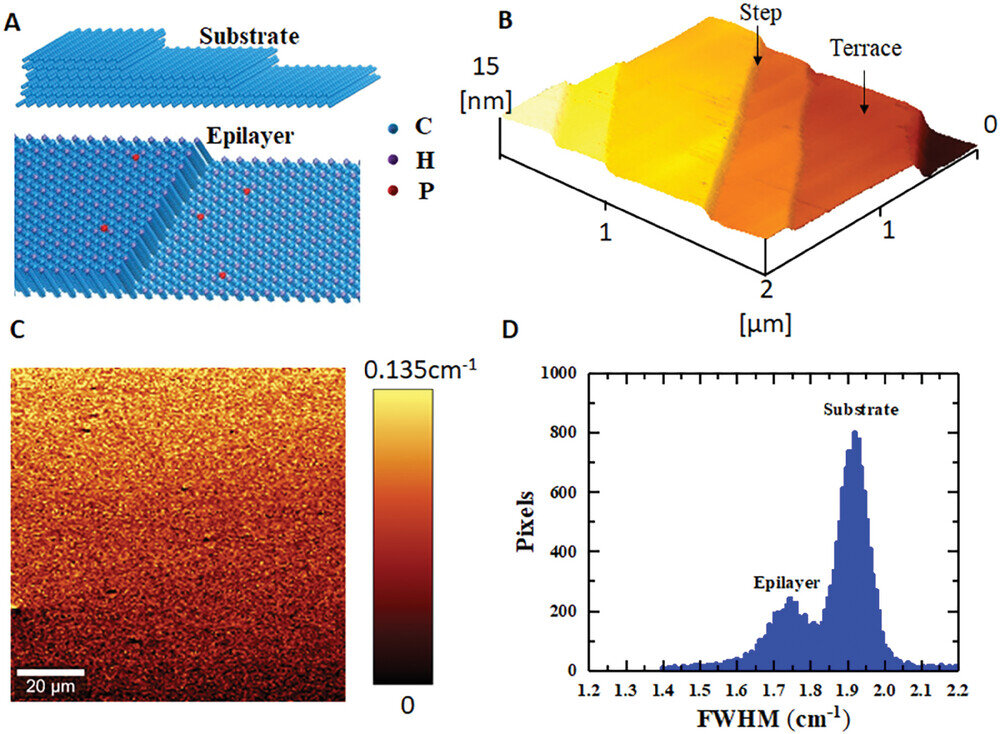

King Abdullah University of Science and Technology (KAUST; Saudi Arabia) researchers have set a record in microchip design, achieving the first six-stack hybrid CMOS (complementary metal-oxide semiconductor) for large-area electronics. With no other reported hybrid CMOS exceeding two stacks, the feat marks a new benchmark in integration density and efficiency, opening possibilities in electronic miniaturization and performance.

A paper detailing the team’s research appears in Nature Electronics.

Among microchip technologies, CMOS microchips are found in nearly all electronics, from phones and televisions to satellites and medical devices. Compared with conventional silicon chips, hybrid CMOS microchips hold greater promise for large-area electronics...

Read More

Recent Comments